フリップフロップ¶

Example

回路ファイルはサンプル回路TOPページからダウンロードできます。

RSフリップフロップ¶

Example

サンプル回路はこちら:Scideam/HowToUse/flipflop/

- RSFlipFlop.scicir

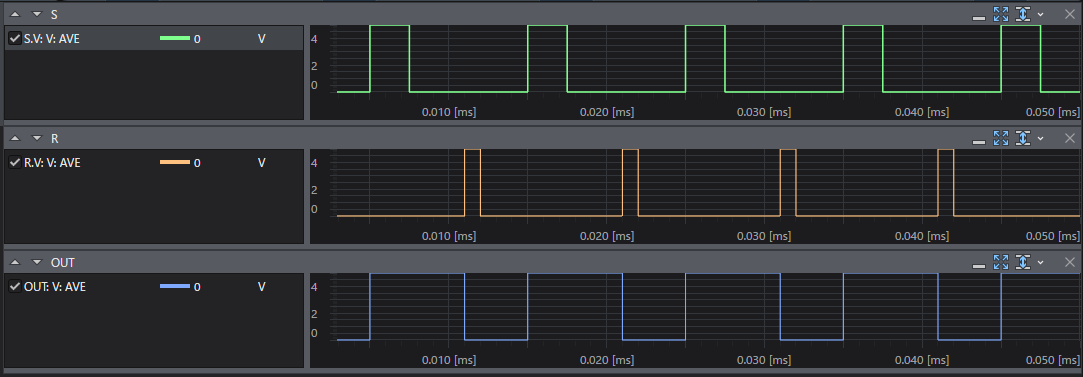

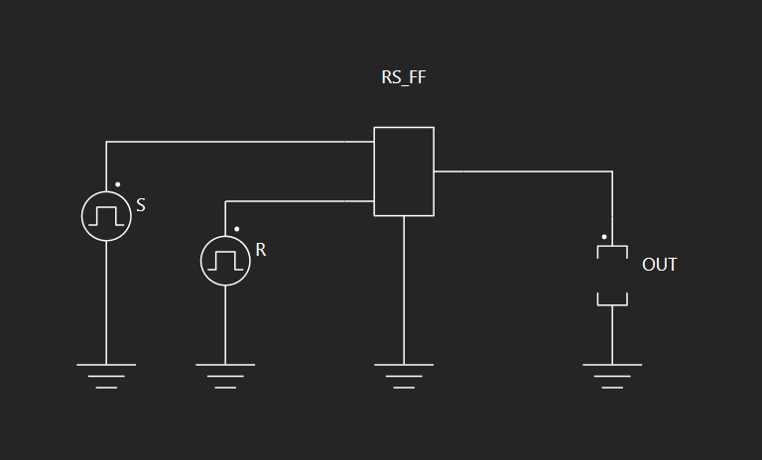

RSフリップフロップの挙動を示します。

本サンプルモデルでは、二つの Pulse によってセット信号 S とリセット信号 R を発生させ出力 OUT の挙動を確認します。

RSフリップフロップは Logic素子のモードを RS-FF とすることでご利用いただけます。

Waveform解析で50u秒シミュレーションすると以下のような結果が得られます。

Dフリップフロップ¶

Example

サンプル回路はこちら:Scideam/HowToUse/flipflop/

- DFlipFlop.scicir

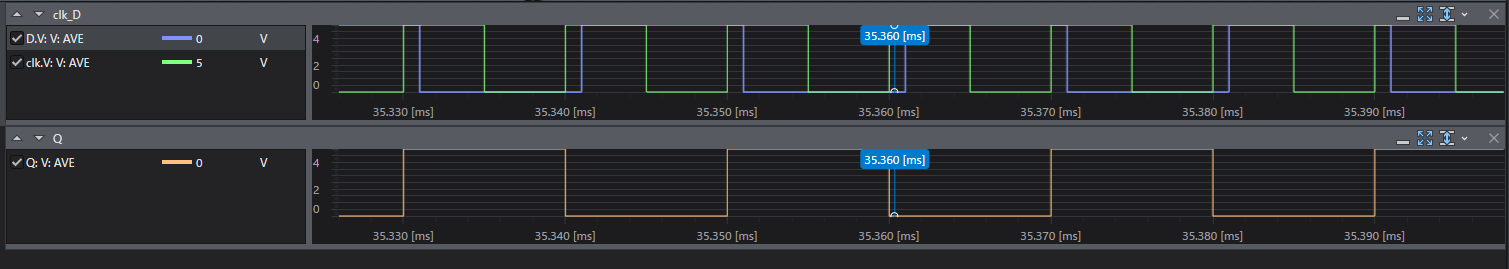

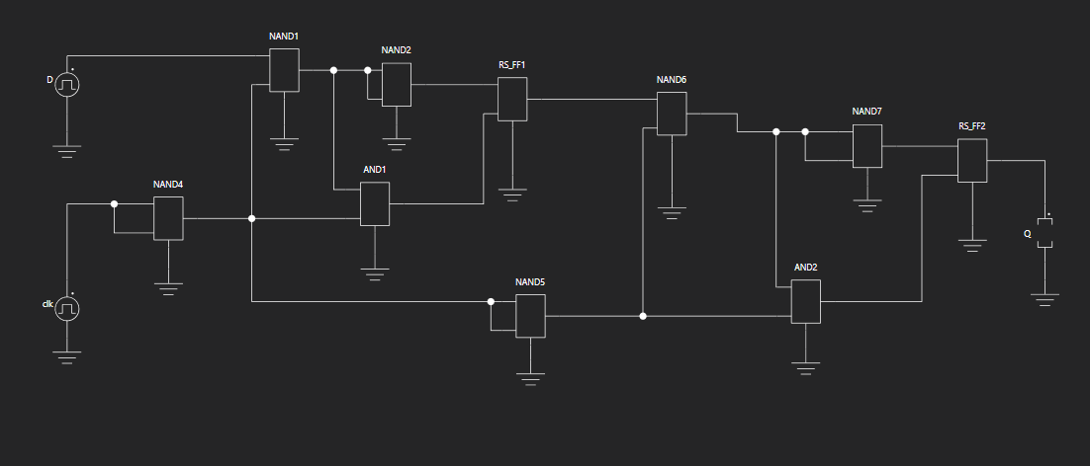

Dフリップフロップは標準素子としては実装されていませんが標準素子を組み合わせることで実装することができます。

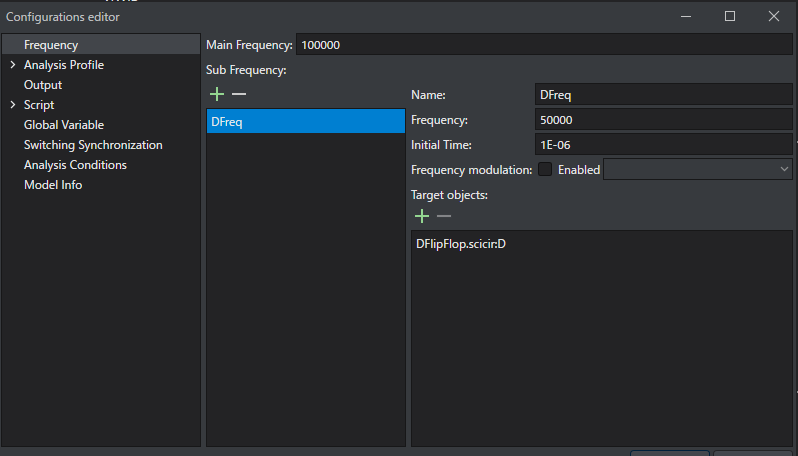

Pulse Dは サブ周波数 DFreqが設定されており、50kHzの周波数で動きます。

Waveformで100u秒シミュレーションすると以下のような結果が得られます。