力率改善回路

Example

回路ファイルはサンプル回路TOPページからダウンロードできます。

サンプル回路はこちら:Scideam/Circuit/pfc/

pfc.scicir

電流臨界モード力率改善回路

電流臨界モード力率改善回路とはインダクタに流れる電流が0Aとなった時に、スイッチングを更新することで電源入力電流の力率を改善する回路のことです。

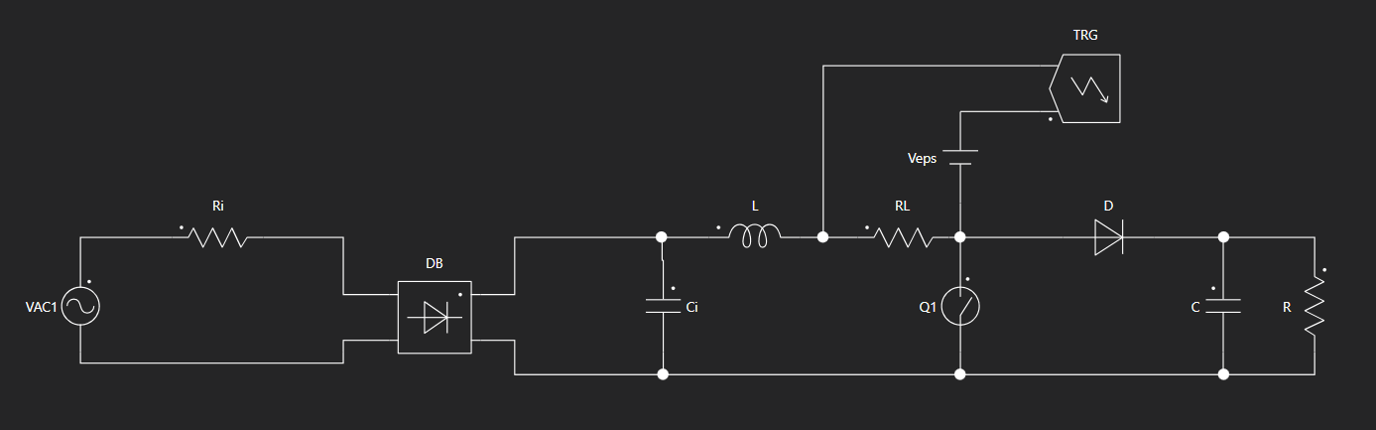

回路は下図のようになります。

サンプル回路ではスイッチングの更新をTriggerを使って行っています。

TRG(Trigger)の正側に非常に小さい電圧(100uV)の電圧源Vepsを接続し、インダクタ電流が0A付近になった際にTRGの入力電流差電圧が負から正になるように設定します。

これによりインダクタ電流が0AとなるタイミングでTriggerがオン状態となり、スイッチングが更新されます。

シミュレーション

シミュレーションは Waveform解析を選択し、シミュレーション時間は50m秒として、シミュレーションを行ってください。

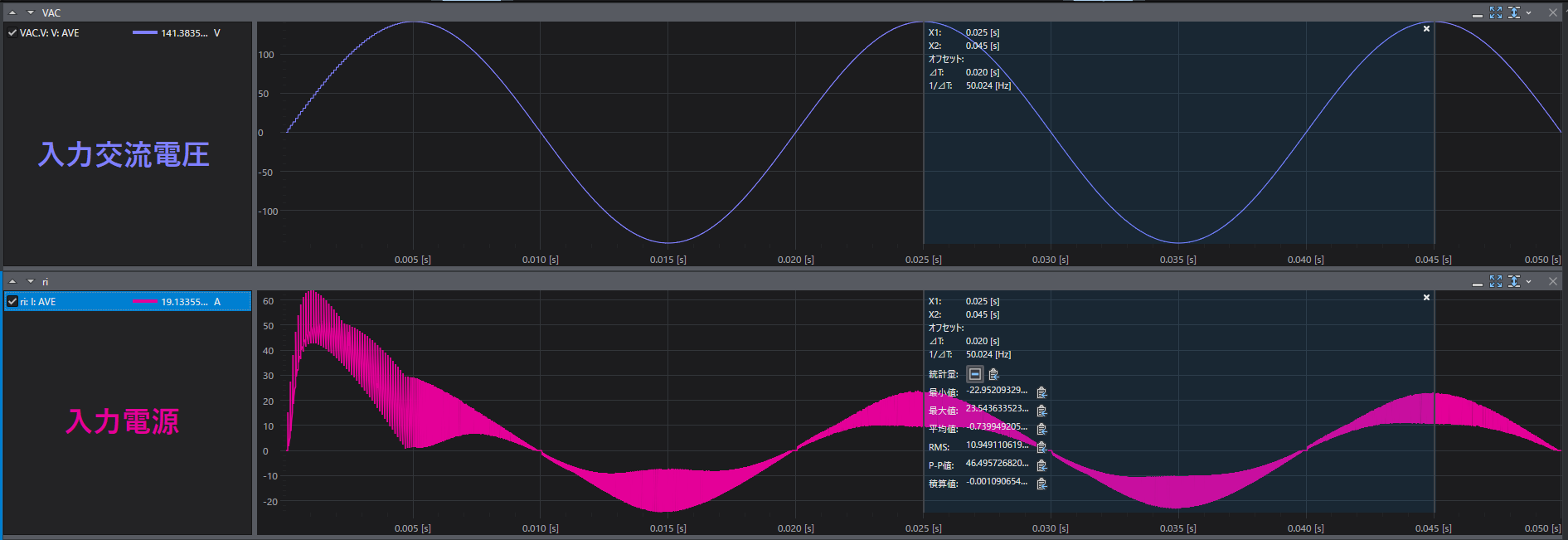

結果は以下となります。 はじめに、入力電圧と入力電流の関係を確認します。 力率改善回路によって入力電流の位相差が軽減され、入力電圧の正弦波に近い形になっていることがわかります。

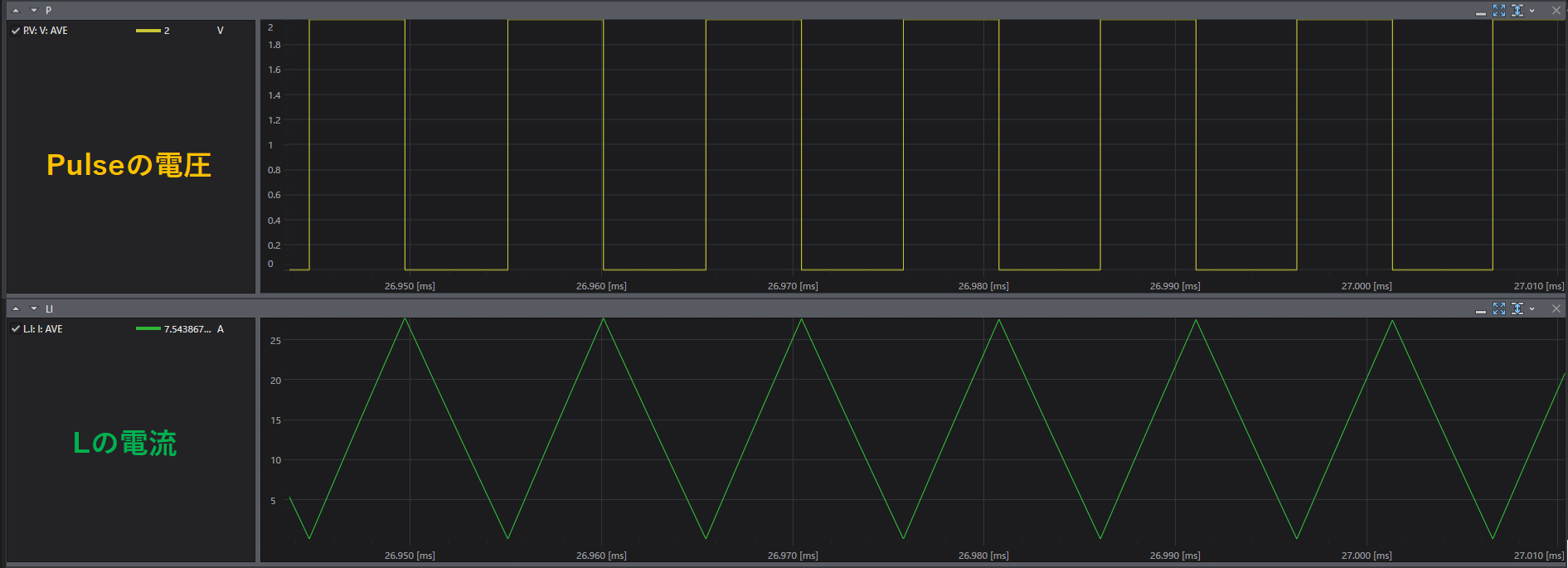

次に定常状態となっている27msec付近を拡大して、Pulseの電圧とL電流を確認してみてください。

L電流が0Aとなった時スイッチオンになっており、電流臨界モードが実装できていることを確認することができます。