チュートリアル:Power Palette編

降圧型DCDCコンバータのサンプル回路「dcdc_converter_loss_sample.scicir」を使用して、損失解析方法について説明します。

Example

-

Kelvin端子なし

power_palette/dcdc_converter/dcdc_converter_loss_sample.scicir -

Kelvin端子あり

power_palette/dcdc_converter/dcdc_converter_loss_fet_kelvin_sample.scicir

Note

回路ファイルはサンプル回路TOPページからダウンロードできます。

1. 回路の読み込み

サイディームを起動し、File > 開くをクリックして「dcdc_converter_loss_sample.scicir」を開きます。

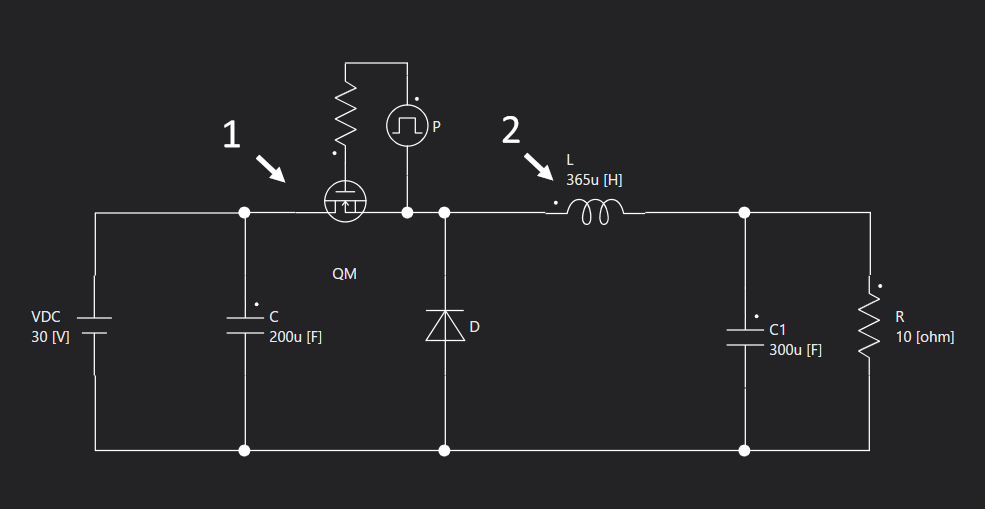

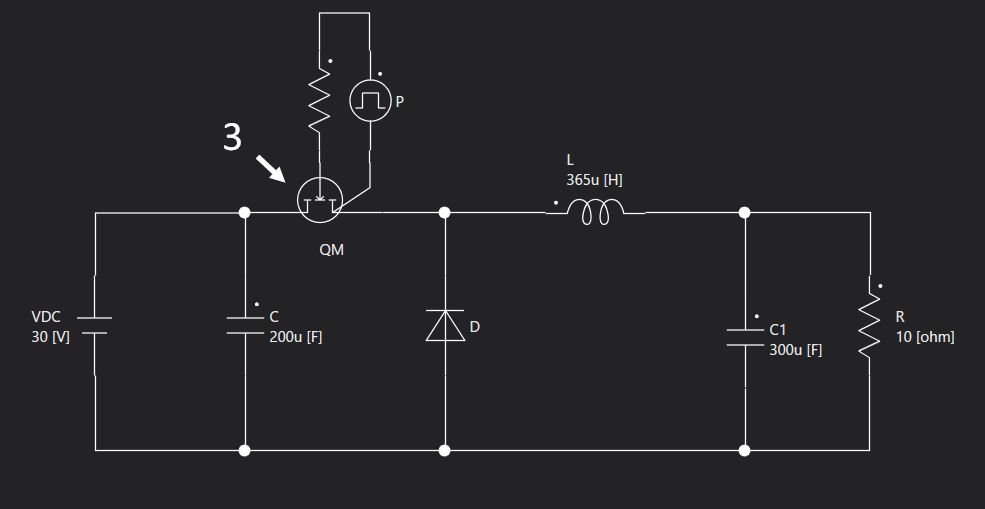

2. 素子の確認

サンプル回路には損失解析に使用される素子が組み込まれています。

Kelvin端子なし

Kelvin端子あり

3. 損失解析前の準備

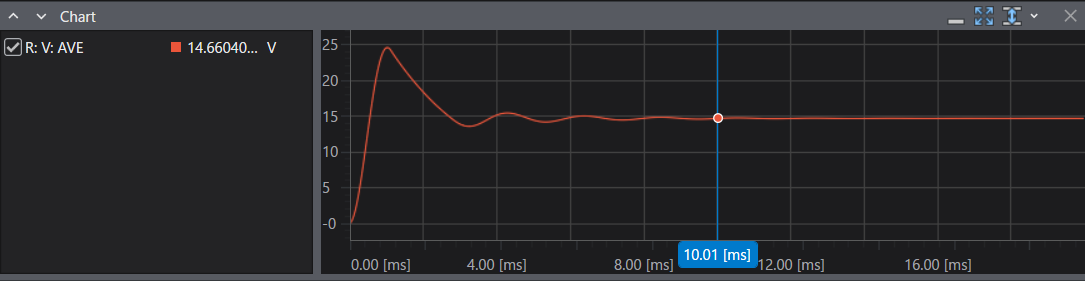

損失解析を行う前に、十分に定常状態にする必要がある為、Transient解析を行い定常状態となる時間を確認します。

3.1 解析方法の選択

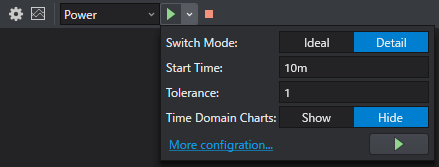

損失解析を行うため、シミュレーションモードはPowerを選択します。

損失解析方法には、理想損失解析と詳細損失解析の2種類の解析方法があります。

理想損失解析では、オン領域とオフ領域の動作領域があり、アクティブ領域は無視されます。

一方、詳細損失解析では、オン領域、オフ領域、アクティブ領域すべての動作領域があります。

理想損失解析を行うには、Switch ModeはIdealを選択します。

詳細損失解析を行うには、Switch ModeはDetailを選択します。

今回はDetailを選択します。

3.2 損失解析開始時間の設定

Start Timeには損失解析を開始する時間を設定します。

事前に確認していた十分に定常状態となる時間を設定します。今回は10mを設定します。

3.3 Toleranceの設定

Toleranceは今回はデフォルト値1のままにします。

Note

パラメータについて詳しく知りたい場合は 損失解析パラメータについて を参照してください。

4. シミュレーションの開始

パラメータの設定が完了したら、実行ボタンをクリックしてシミュレーションを開始します。

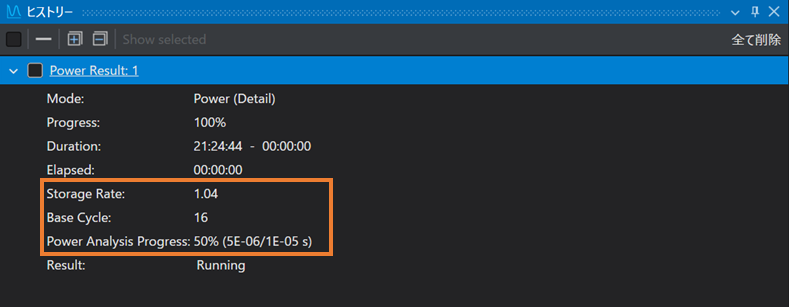

4.1 シミュレーションの進捗

損失解析シミュレーション中の、収束状況はヒストリーウィンドウに表示されるStorage Rate値で観測できます。

Storage Rate < Tolerance の条件を満たすと損失解析が終了して結果が表示されます。

Note

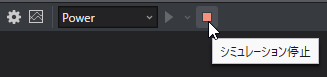

損失解析がなかなか収束しないなどの理由で、解析を中断したい場合は、回路エディタのツールバーの停止ボタンをクリックします。

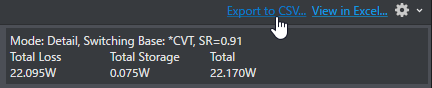

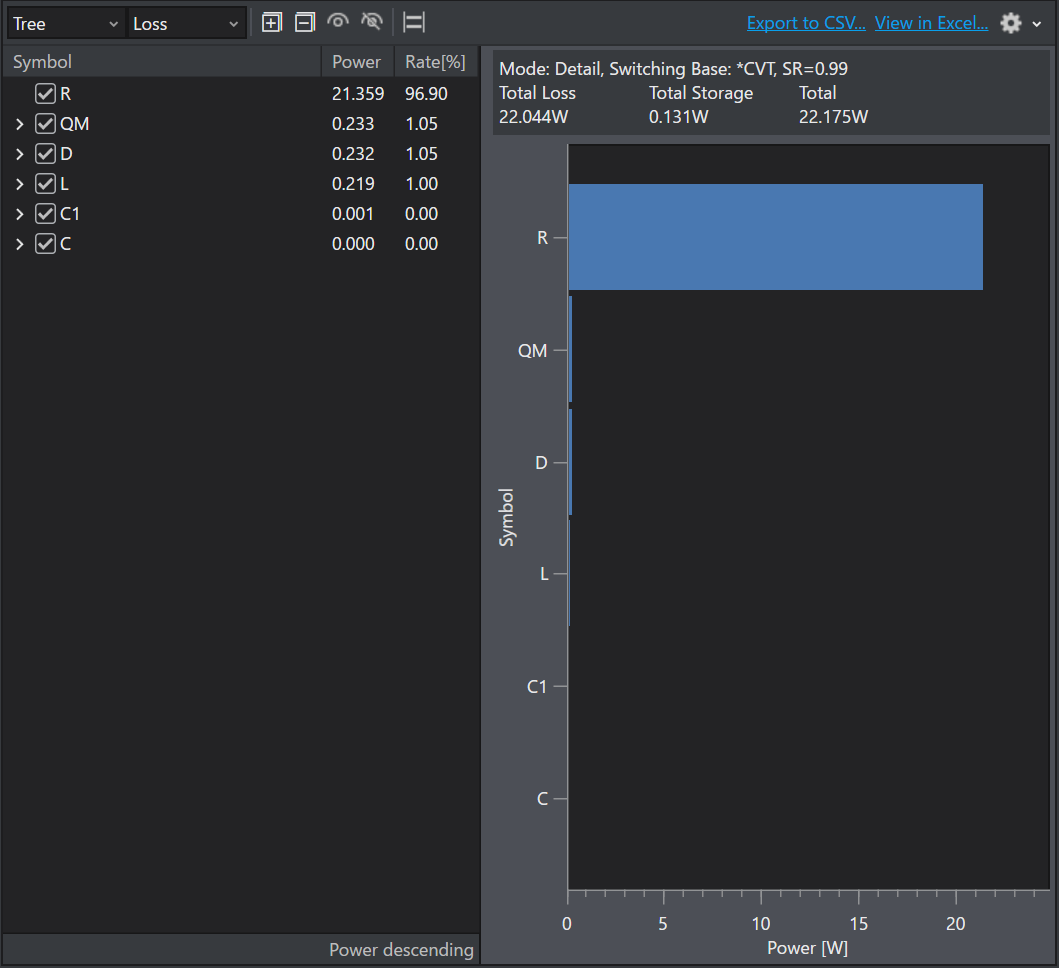

5. シミュレーション結果の確認

シミュレーションが完了すると、結果リストビューワーが立ち上がります。

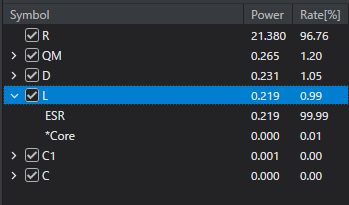

5.1 素子内部の損失を確認する

素子内部の損失を確認するには、シンボルの左端の>をクリックして展開します。

Note

各素子の内部要素構成は下記ページを参照してください。

損失成分を持つ素子と内部構造について

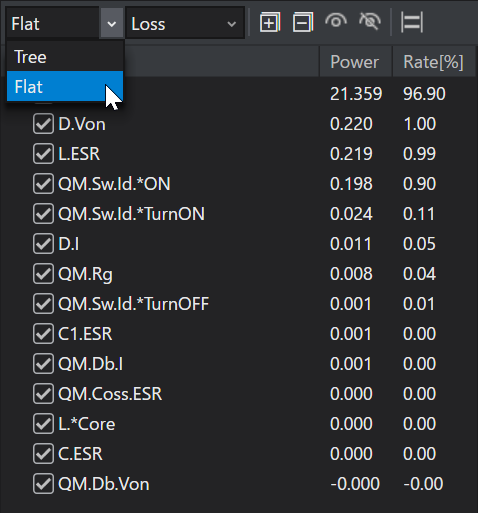

5.2 内部損失を一覧表示する

リスト上部のツールバーでで表示方法を変更することができます。

Flatに変更すると内部要素も含め、階層表示から一覧表示に変更することができます。

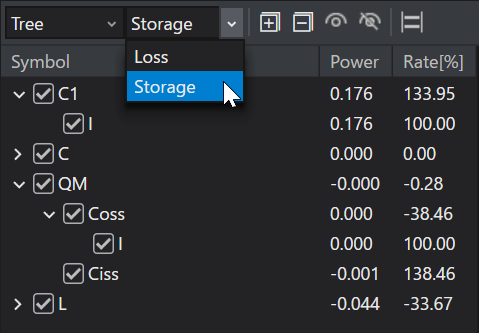

5.3 LCに蓄えられている電力

LCに蓄えられている電力を確認するには図のようにStorageを選択します。

-の値は電力が放出されていることを意味します。

5.4 リストをエクスポートする

シミュレーション結果はCSV形式でファイルに保存することもできます。