ゲートブロック

Note

回路ファイルはTOPページからダウンロードできます。

プログラムによるゲートブロック

Example

gate_block/GateBlock.cvt2

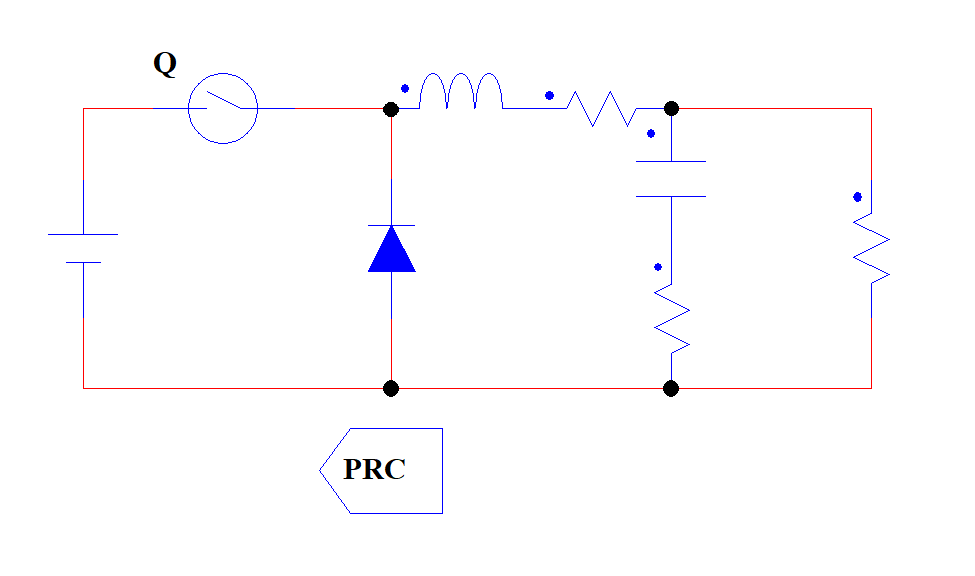

回路は下図のようになります。

PRCのプログラムによってゲートブロックフラグが立っているときQのオン抵抗値をオフ抵抗と同等の値にすることで、

時比率の指令値によらず、常にオフ状態となりゲートブロックを実現します。

PRC素子のプログラムは下記となります。

Duty = 0.5;

GateBlock = 1;

setparam("Q","T0",Duty);

setoutvar(Duty);

if(GateBlock ==1)

{

setparam("Q","Ron",1M);

}

else

{

setparam("Q","Ron",100m);

}

なお、このサンプル回路ではゲートブロックフラグが固定値となっています。

実際に使用する場合は外部からゲートブロックフラグを受け取るように変更してご使用ください。

継続解析を使用したゲートブロックのシミュレーション

Example

gate_block/GateBlockContinue.cvt2

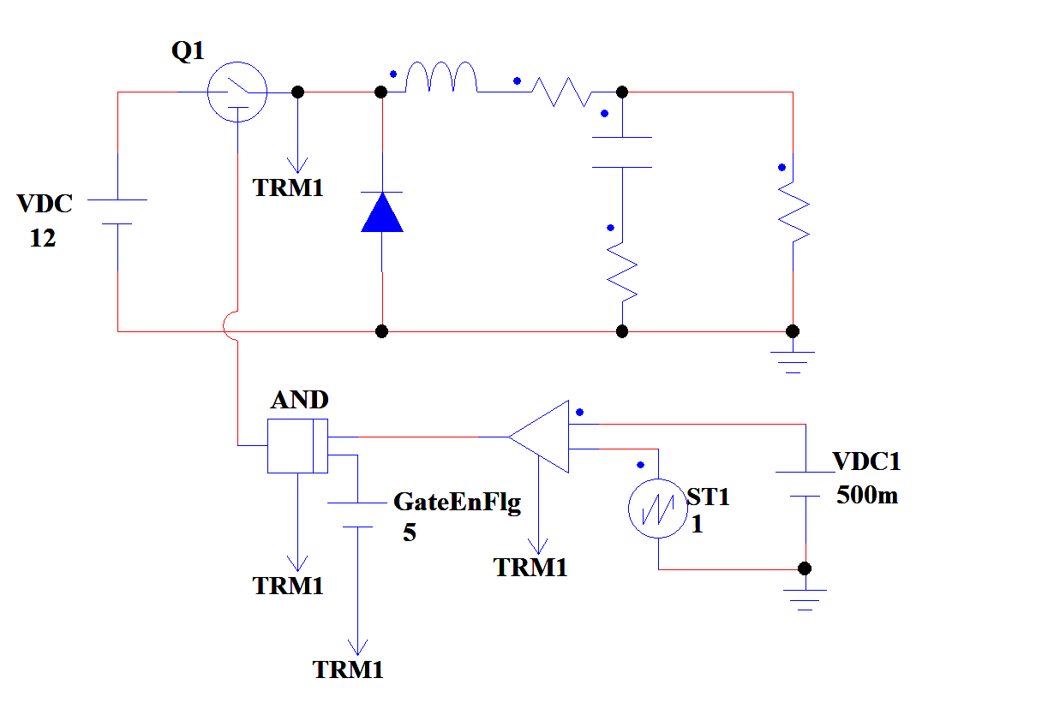

回路は下図のようになります。

継続解析を使用することで、シミュレーション途中に与えれるゲートブロックフラグを簡単に再現させることができます。

-

ゲートブロックフラグが変化するポイントまでゲートがONの状態でのシミュレーションを行います。

Waveformを用いて500usシミュレーションを行ってください。

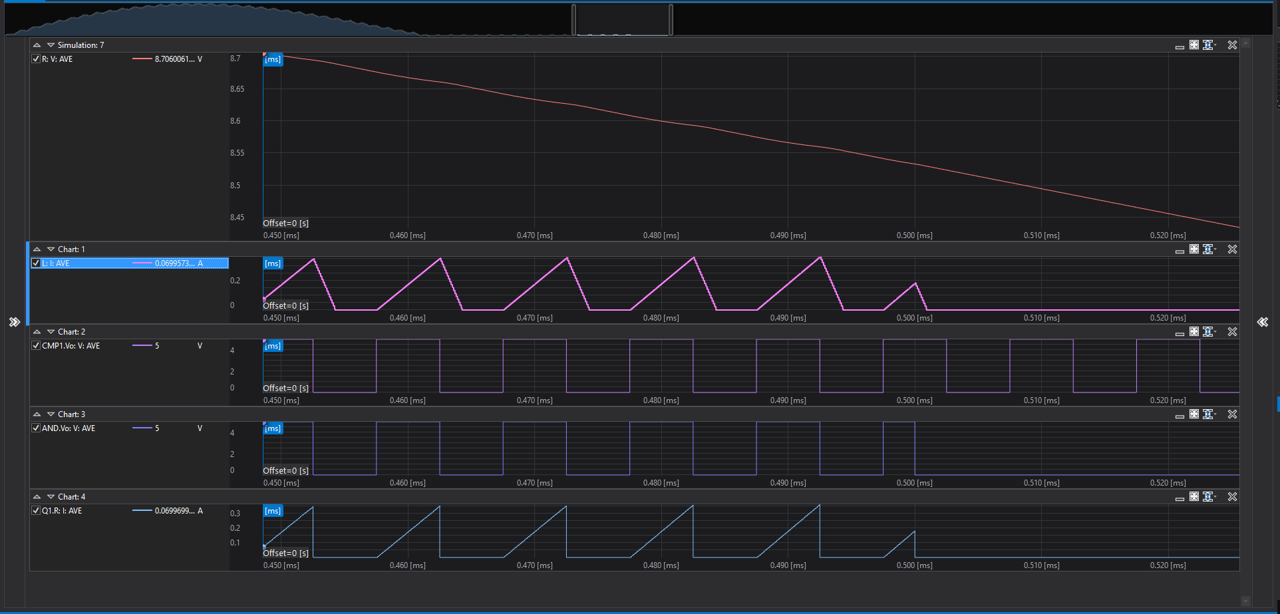

出力される波形は次のようになります。(解説のため、データごとにチャートを分けていますが、実際は継続解析後にチャート分けを行ってください。) -

waveformによるシミュレーション後、ゲートブロックフラグGateEnFlgの値を0としてください。

直前のコンパレータのON時の電圧は5VなのでGateEnFlgを0とするとLogic素子ANDの出力値が

False側の値となり、ゲートブロックの状態となります。 -

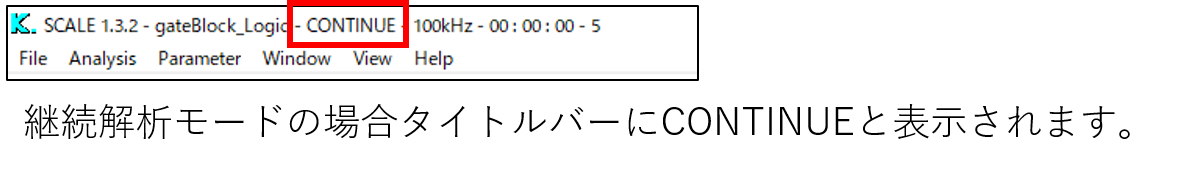

継続解析を行うには

Analysis:ContinueまたはSpaceを押すことで継続解析モードとなります。 この状態で再度シミュレーションを行うことで、前回のシミュレーション後の状態を継続して解析を行うことができます。

-

継続解析モードに切り替えた状態で再度

Waveformで500usシミュレーションを行ってください。

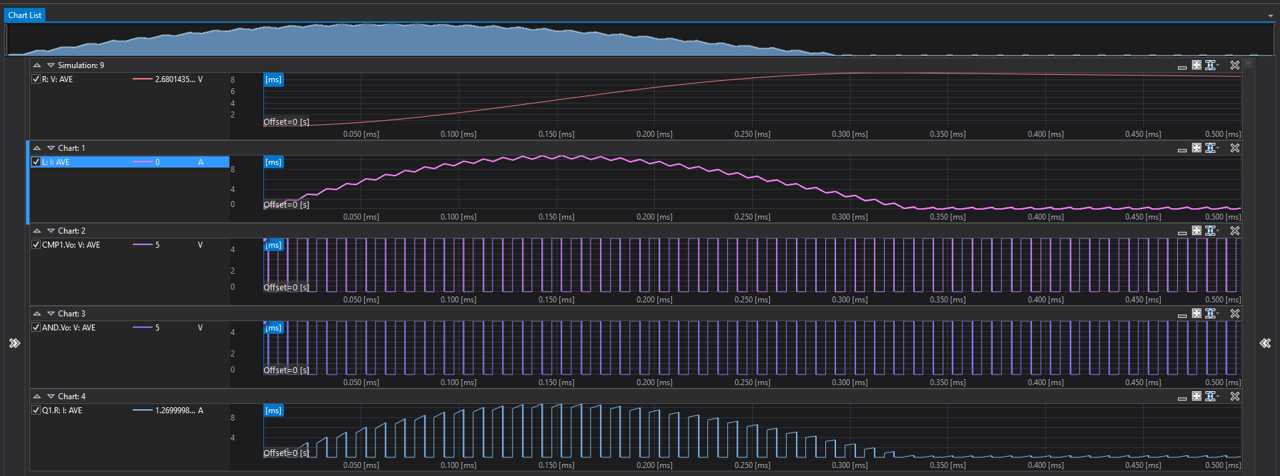

シミュレーション結果は次のようになります。 L:Iの値を見ると分かるようにゲートブロック後波形の揺れがなくなっていることが確認できます。